alARM is a simple ARM-like ISA used an assignment for the UC Davis computer architecture course.

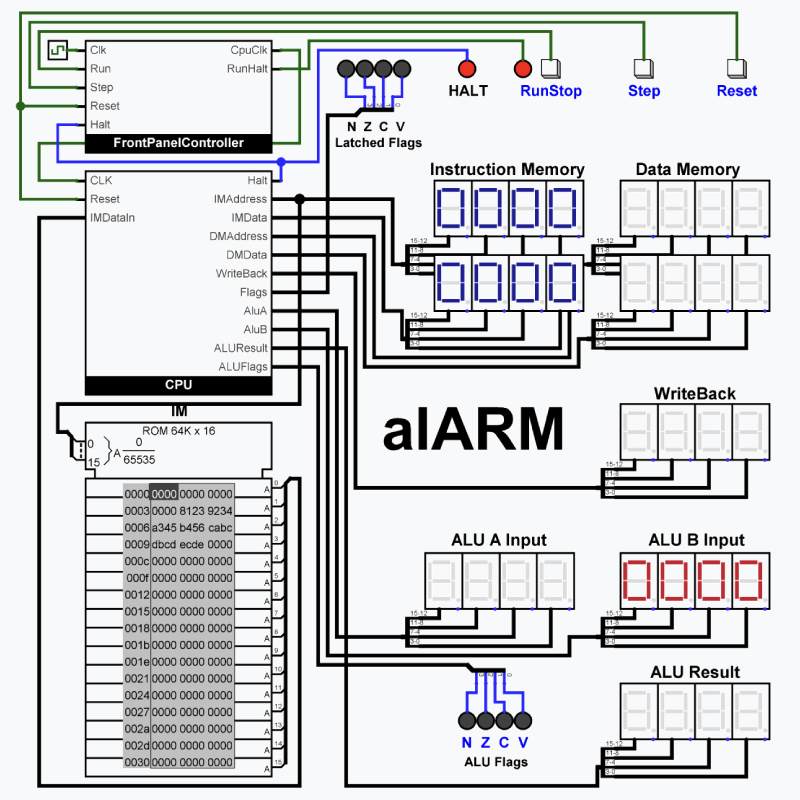

The assignment specified a digital logic simulation of an alARM CPU to be made in the program Logisim. The design and implementation of this CPU is documented in the whitepaper linked below.

The original assignment required hand-assembling programs into the bytecode so that it could be loaded into Logisim. As a student in the class, I volunteered to write an assembler for the rest of the class to use to speed up this tedious process. The assembler includes a choice of strict or relaxed syntaxes, highly informative error messages, and pseudo-instructions. You can see a full specification of the assembly syntax in the assembler's README.

The assembler was written to gracefully handle the addition of new instructions and pseudo-instructions -- this proved useful when students in future iterations of the class forked and easily updated the assembler for new project specifications.